Este site pode ganhar comissões de afiliados dos links nesta página. Termos de uso.  (Crédito: Intel) Na conferência HotChips 34 desta semana, o CEO da Intel, Pat Gelsinger, apresentou a visão de sua empresa para o futuro, e um dos pilares dessa visão é a embalagem avançada que combina vários chiplets. Isso não é uma surpresa para ninguém, mas também fala de sua ênfase em suas próximas CPUs Meteor Lake baseadas em blocos, que a empresa discutiu antes da palestra de Gelsinger. No entanto, o CEO detalhou seus pensamentos sobre como isso afetará a indústria de semicondutores em geral. Uma das principais características, disse ele, é que permitirá que a Lei de Moore prospere bem na próxima década. Ele acha que isso permitirá um aumento de 10 vezes na densidade de transistores até 2030. Isso deve permitir que a Intel amplie até um trilhão de transistores em um chip.

(Crédito: Intel) Na conferência HotChips 34 desta semana, o CEO da Intel, Pat Gelsinger, apresentou a visão de sua empresa para o futuro, e um dos pilares dessa visão é a embalagem avançada que combina vários chiplets. Isso não é uma surpresa para ninguém, mas também fala de sua ênfase em suas próximas CPUs Meteor Lake baseadas em blocos, que a empresa discutiu antes da palestra de Gelsinger. No entanto, o CEO detalhou seus pensamentos sobre como isso afetará a indústria de semicondutores em geral. Uma das principais características, disse ele, é que permitirá que a Lei de Moore prospere bem na próxima década. Ele acha que isso permitirá um aumento de 10 vezes na densidade de transistores até 2030. Isso deve permitir que a Intel amplie até um trilhão de transistores em um chip.

A maior mudança, de acordo com os comentários de Gelsinger via The Register, está se afastando da noção de que as fundições apenas produzem wafers. Em vez disso, ele vê esse serviço evoluindo para fornecer um”sistema”inteiro para os clientes. Esse sistema inclui fornecer o wafer junto com vários blocos, embalagens avançadas e software para unir tudo. Para descrever essa evolução, Gelsinger diz que fornecerá Descrevendo um rack em um data center, Gelsinger explicou, “quando digo que o rack está se tornando um sistema, o sistema está se tornando um SOP avançado baseado em chiplet, é exatamente isso que queremos dizer e como veja isso evoluindo.”

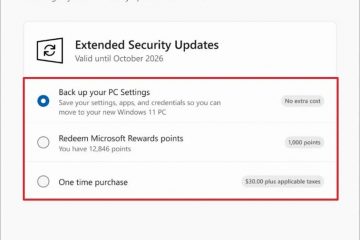

Intel’s visão para o aumento da densidade do transistor ao longo dos próximos oito anos. (Imagem: Intel)

Parte dessa evolução envolve a redução de nós junto com o empilhamento de matrizes, que a Intel já discutiu. Em 2024, a Intel desistirá do FinFET e passará para os transistores RibbonFET gate-all-around (GAA). Este será o seu nó de 20A, já que a Intel abandona a nomenclatura nanométrica para Angstroms. Ao mesmo tempo, também está introduzindo o PowerVIA, que é a entrega de energia traseira. Gelsinger acredita que essa mudança, juntamente com os avanços na embalagem, abrirá o caminho para avanços desenfreados na densidade de semicondutores.

“Hoje, existem cerca de 100 bilhões de transistores em um pacote, e vemos nosso caminho claro para chegar a um trilhão transistores até o final da década”, disse ele.”Com a fita FET, temos uma nova estrutura fundamental de transistor que estamos prestes a entrar, que acreditamos que continuará a crescer até o final da década.”

Gelsinger também acredita que a tecnologia de combinação que está usando para o Meteor Lake é o futuro. Isso significa combinar diferentes chips, ou ladrilhos, construídos em diferentes nós com base no que é mais eficiente. Como exemplo, o Meteor Lake combinará quatro nós de processo diferentes em sua própria fundição e nos TSMC. Ele estará construindo o interposer base em seu processo de 22nm e o bloco de CPU no Intel 4 (anteriormente 7nm). Enquanto isso, a TSMC fará o SoC, E/S e GPU em seus próprios processos N5 e N6.

“Você pode dizer, ei, estou recebendo dois chiplets da Intel, estou recebendo um dos chiplets de uma fábrica TSMC, talvez os componentes da fonte de alimentação da TI, talvez haja um componente de E/S vindo da Global Foundries e, claro, a Intel tem as melhores tecnologias de empacotamento, então eles vão montar todos esses chiplets juntos , mas talvez seja outro fornecedor de montagem também, então vemos essa mistura e combinação acontecendo”, disse Gelsinger.

Gelsinger provavelmente está certo sobre a embalagem se tornar a vantagem dominante que uma fundição tem sobre outra. À medida que a matriz encolhe se tornarem menos frequentes e os chiplets passarem para a vanguarda, como essas peças se encaixam será uma tecnologia crucial nos próximos anos. Para esse fim, a Gelsinger também divulgou seu conector chiplet universal baseado em PCI Express. É apropriadamente chamado, você adivinhou, Universal Chiplet Interconnect Express (UCIe). Este é um consórcio liderado pela Intel que busca padronizar a mistura e combinação de chiplets de várias fundições. Inclui alguns dos maiores nomes do mundo dos semicondutores, incluindo AMD e Qualcomm. Notavelmente ausentes estão Apple e Nvidia.

Se esta será uma estratégia vencedora para a Intel continua a ser visto. Porém, descobriremos em breve, pois a Intel confirmou que o Meteor Lake está no alvo para 2023 na mesma conferência. Este será o primeiro design de chip “desagregado” da empresa, apresentando os azulejos mencionados acima de duas fundições diferentes. Além disso, essa mistura e combinação foi supostamente a causa de rumores de atrasos para Meteor Lake, o que revela uma falha na estratégia. Se alguns blocos estão sendo feitos em nós avançados e não estão todos prontos ao mesmo tempo, surgem problemas. A Intel negou esses rumores e diz que ainda está dentro do cronograma.

Agora leia: